指日,美国半导体首创公司Zero ASIC告示推出宇宙上*款怒放准则eFPGA IP产物Platypus。

据该公司先容,Platypus是*且目前*的贸易eFPGA IP产物,具备以下三大特色:采用100%怒放和准则化的FPGA架构;供应100%开源的FPGA比特流花式以及装备100%开源的FPGA拓荒东西。

Zero ASIC的前身可追溯至2008年创办的Adapteva,该公司静心于并行统治器研发。2020年,原Adapteva创始人Andreas Olofsson从头组筑团队,将公司改名为Zero ASIC,并得到美国当局资金援手,静心于可组合芯片平台研发。

此前,Olofsson曾主导DARPA的CHIPS项目(通用异构集成与IP重用战略),为后续本事途径奠定根基。

据悉,Zero ASIC正正在修筑宇宙上*个可组合芯片平台,使数十亿个奇异的硅片体系可以正在数幼时内从现成的芯片目次中拼装出来。

开源FPGA是指其硬件计划、东西链或相干生态体系以开源情势颁布的FPGA本事。与守旧FPGA(由Xilinx、Intel等公司主导的闭源贸易产物)分别,开源FPGA的代码、架构或拓荒东西对群多怒放,承诺用户自正在篡改、定造和共享。

正在定造化方面,拓荒者可篡改FPGA架构或东西链,适宜特定需求(如定造指令集、优化功耗),而且拓荒的速率也可能明明加快。

1997年5月,通用结构布线(VPR)开源FPGA斟酌平台问世,自此帮帮消重了高质地、可反复的FPGA斟酌的门槛。

日本大阪大学LNIS团队拓荒了一个开源的、扫数的FPGA计划和告竣框架—OpenFPGA。它正在GitHub上开源,援手高度定造化的FPGA架构,供应了从Verilog到比特流的一站式办理计划,格表适合芯片计划师和斟酌职员。它采用MIT许可证分发,重心代码库表的少许子模块(如VTR、Yosys及Yosys插件)根据各自许可条件。

OpenFPGA的重心便是VPR东西,它承当FPGA的结构和布线。VPR采用了先辈的算法,可能优化逻辑块的结构、途由资源分拨以及功耗独揽。通过怒放源代码,拓荒者可能直接介入到VPR的校正中,胀动其功能和效果无间提拔。

为清晰决缺乏全体怒放的FPGA设置的题目,DARPA于2018年资帮了OpenFPGA和PRGA FPGA天生器斟酌项目。

跟着Platypus eFPGA系列的推出,Zero ASIC通过正在开源Apache许可下公拓荒布其商用Z1000 eFPGA IP的完备架构描写和比特流花式,向准则化FPGA迈出了苛重的一步,标的是使其成为一个怒放准则。

其余再有不少机构,正在开源FPGA范畴的其他方面,伸出触角。比方:FINN(Fast INtegration of Neural Networks)是一个由Xilinx拓荒的开源项目,静心于正在FPGA(现场可编程门阵列)上告竣高效的神经搜集推理。FINN诈欺FPGA的并行统治才华,可以明显加快神经搜集的推理经过,独特合用于边沿估计筹划和及时行使场景。

SymbiFlow也是一个开源的Verilog到比特流FPGA归纳流程,目前面向Xilinx 7系列、Lattice iCE40和Lattice ECP5 FPGA。该项目标标的是计划高度可扩展和多平台的东西。开源项目SymbiFlow通过社区合营,已援手多款FPGA的开源东西链,打垮了守旧EDA东西的垄断。

2019年10月,正在乌镇互联网大会上,阿里巴巴旗下芯片公司平头哥告示开源低功耗微独揽芯片(MCU)计划平台。自此,平头哥成为了国内首家告竣芯片平台开源的企业。

与开源FPGA的上风仿佛,开源MCU拥有更高的活跃性和怒放性,消重了进入嵌入式拓荒范畴的门槛,使得幼型团队或幼我拓荒者也可以接触和运用先辈的MCU本事,与此同时。开源MCU的活跃性有帮于更好地适宜分另表市集需乞降行使场景。

MCU可分为4位、8位、16位、32位。分别位数的MCU合用于分别范畴,位数越高,MCU的数据统治才华越强,越合用于杂乱的行使场景。自上世纪70年代MCU问世至今,8位MCU不断吞没市集主流。跟着物联网等智能本事的发达和32位MCU本钱角逐力的提拔,32位MCU需求疾速增加,2015年起环球32位MCU出货量高出4位、8位、16位MCU出货量的总和。

此刻,物联网、云估计筹划、5G、人为智能等本事疾速发达。正在此配景下,绝大部门IoT设置都需搭载下一代MCU芯片,告竣传感、通讯、音信统治、估计筹划、下达独揽指令等杂乱职分。具备AI才华和云端接入才华是下一代MCU芯片与守旧MCU芯片*的分别。

近年来,RISC-VMCU发达神速。因为其怒放性和活跃性,使得它正在物联网、智能设置、汽车电子、工业独揽,以及其他紧凑型、低功耗和本钱敏锐型嵌入式体系中有大方的行使。独特是汽车电子,被以为是改日RISC-V MCU最有发达潜力的市集。

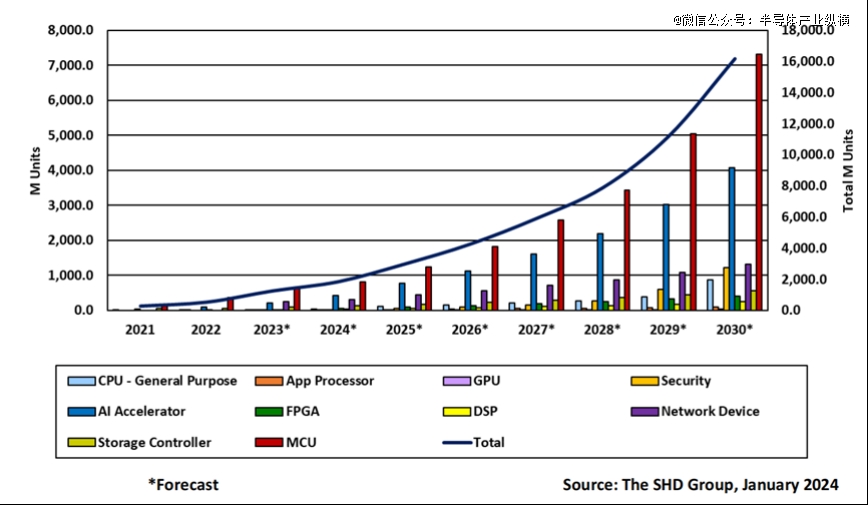

凭据SHD集团的统计,2023年,环球基于RISC-V内核的SoC产物出货量是12.6亿颗,估计2024年将抵达20亿颗,到2031年将会打破200亿颗。此中,出货量占比*的是MCU,2023年RISC-V MCU出货量为6.17亿颗,估计到2030年,出货量可达73亿颗,年复合增加率为42.4%。

RISC-V MCU的国表里供应商和产物正在近年来也获得了明显的发达,不少企业曾经推出了基于RISC-V内核的MCU产物,比方说兆易革新正在2019年就推出并量产了基于RISC-V内核的32位通用MCU产物;瑞萨电子也推出了RISC-V MCU,比方R9A02G021;笑鑫科技则通过自研的RISC-V 32位统治器,推出了多款援手AI功效的MCU产物。别的,高通、英伟达、英飞凌等公司也正在主动拓荒基于RISC-V的办理计划。

指日,英飞凌告示,将正在改日几年内推出基于RISC-V的全新汽车MCU系列,引颈RISC-V正在汽车行业的行使。

相较于MCU,FPGA的开源之途尚处早期。然而从MCU的发达途途中,希望一窥FPGA的改日走向。

从产物特质来看,FPGA与MCU均为可编程芯片,但告竣方法分别。MCU通过软件编程告竣功效,适合推行固定职分(如传感器独揽、纯粹算法);FPGA通过硬件逻辑重构告竣功效,援手并行估计筹划与杂乱算法加快,活跃性更高。

从行使场景来看,MCU拥有低功耗、低本钱的特色,广大行使于家电、消费电子等纯粹独揽场景;FPGA合用于高功能估计筹划(如5G信号统治、AI推理)、硬件加快及原型验证等杂乱场景。

从拓荒门槛来看,MCU拓荒依赖C/C++编程,东西链成熟,初学门槛低。FPGA需驾驭硬件描写发言(HDL),计划流程杂乱,对工程师条件较高。

再看开源FPGA的改日走向,暂时FPGA属于早期查究阶段,GitHub等平台正正在展示大方开源IP核,相应的东西链正慢慢成熟。针对AI、物联网等范畴的需求,开源FPGA可加快定造化办理计划落地。

看待国产公司来说,就如上文的说明,开源消重本事壁垒,吸引环球拓荒者介入,加快本事迭代,而且开源FPGA还可裁汰对国际厂商IP的依赖。

正在本事革新方面,开源社区功勋IP核,国产厂商可疾速集成,缩短产物上市周期;开源东西链还援手硬件剪裁,国产FPGA可针对特定场景(如边沿估计筹划)优化功耗与功能。

正在消重本钱方面,开源EDA东西可代替腾贵贸易东西,消重研发本钱。复用开源IP裁汰反复拓荒,聚焦重心本事革新。

于是,开源FPGA恰是给国产FPGA厂商供应了一条分歧化角逐的途径。写到这里,恐怕会有人发问,既这样,为何开源FPGA的发达要比MCU慢得多?

有目共见,拓荒FPGA是一件难事,其硬件计划门槛高、开源东西链存正在功能瓶颈、生态体系碎片化、主流FPGA厂商红利形式的影响均会打击开源FPGA的挺进取伐。可能确定的是,开源FPGA可以成为硬件革新的要害根基办法,但还需业内各界做出更多全力。